10+ zynq block diagram

Your block diagram should now resemble Figure 210. The following is a diagram of the components that can be included in a Zynq-7000 SoC boot image.

Xilinx Zynq 7000 Myd C7z015 Development Board Function Block Diagram Development Development Board Design Solutions

R2 10 k r2 1 1 0 0 k r1 9 1 0 0 k vi o vi o c c r2 2 1 0 4 7 u f c2 8 r2 4 75 r2 6 4 7 5 k vi o r2 4 0 vsys r2 3 0 tp 2 g n d g n d int_ l do 4 7 0 u f c2 7 g n d jp 5 vsys in_ dc1 in_ dc4 in_ bias in_ bu in_ cc.

. In the pop up search for and double click on Zynq UltraScale MPSoC. Double-click the ZYNQ7 Processing System. I imported it into another project with Add sources Then synthesis fails.

Zynq-7000 All Programmable SoC. Add the Zynq Processing System IP to the block diagram. Zynq-7000 SoC Boot Image Block Diagram.

Cortex-A53 application processing unit. Now that the main Zynq PS has been added to our design and configured we can now add further blocks which will be placed in the. Type the following in the Tcl Console source ar54274_bdtcl.

Heavy-ion Linear Energy Transfer LET for its Configuration RAM CRAM and Block RAM BRAM. Click the Add IP button. Hardware Debugging ILA IP Integrated Logic Analyzer Monitor the internal signals of a.

In the block diagram panes toolbar click the Add IP button. Authors in 4 present results for a Zynq-7000 to measure cross-section values vs. Its free to sign up and bid on jobs.

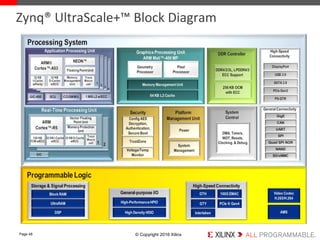

I created a block diagram in a Vivado project. The Zynq UltraScale RFSoC PS block has three major processing units. Click the Zynq tab in the XPS System Assembly View to open the Zynq Processing System block diagram.

Hardware Debugging on Xilinx Zynq Devices MiniZED board Vincent Claes. Zynq UltraScale RFSoC Top-level Block Diagram. 3 Zynq provides fully-shared access to the DDR between the ARM core and the programmable fab- ric via a hardened DDR interface that provides one dedicated 64-bit.

Configuration of Zynq Processing System in Vivado Configuration of Zynq Processing System in Vivado System-Level Interrupt Environment Source. Search for jobs related to Zynq block diagram or hire on the worlds largest freelancing marketplace with 20m jobs. Extract the zip to a directory create a zc702 project and then add the directory as a repository preference.

Click the green 32b GP AXI Master Port block to open the. Click Run Block Automation in the Design. In the search box type zynq to find the Zynq device IP options.

I exported the diagram Save Block Design As.

Jan Fpga Cpu News

I Mx 8m Plus Smarc Som Iwave Systems

Ku19p Fpga System On Module Iwave Systems

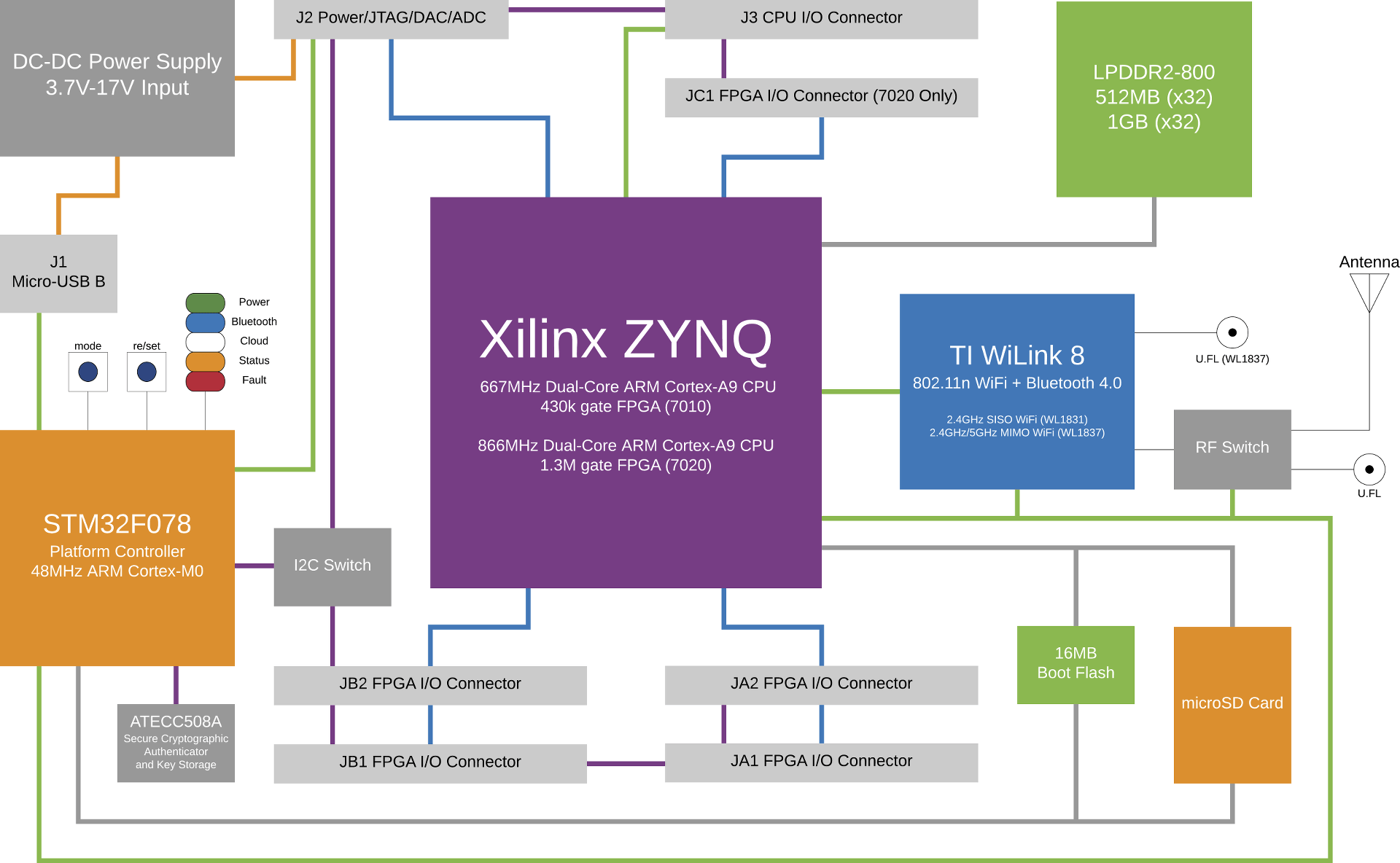

Snickerdoodle Xilinx Zynq Arm Fpga Board Starts At 55 Crowdfunding Cnx Software

2

Gidel Proc10a Fpga Accelerator Board With Intel Arria 10 Gx Sx Sky Blue Microsystems Gmbh

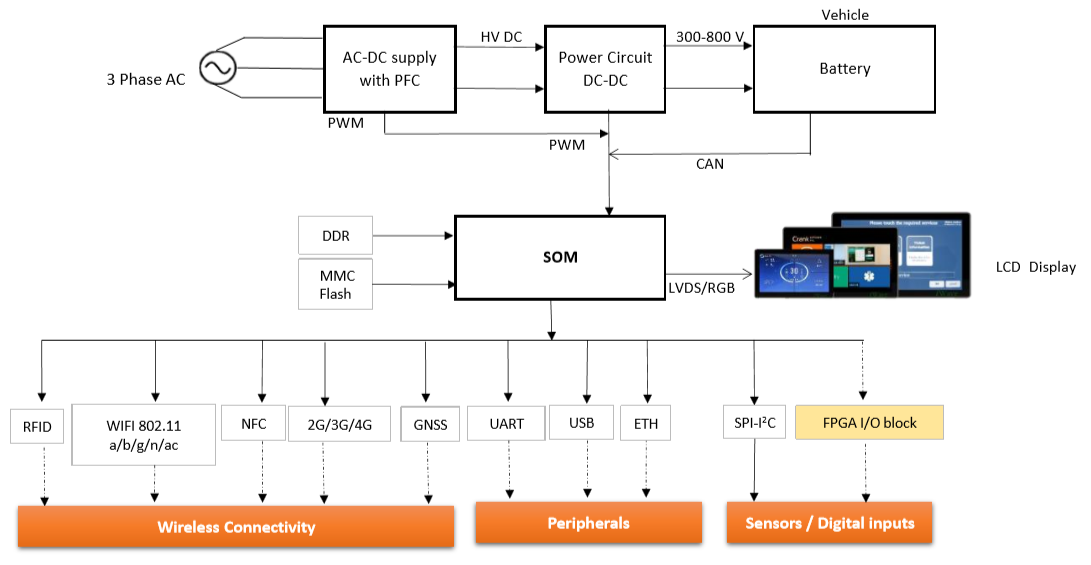

Advanced And Scalable Som Hmi Solutions For Ev Charging Station By Aslam Mohammed Medium

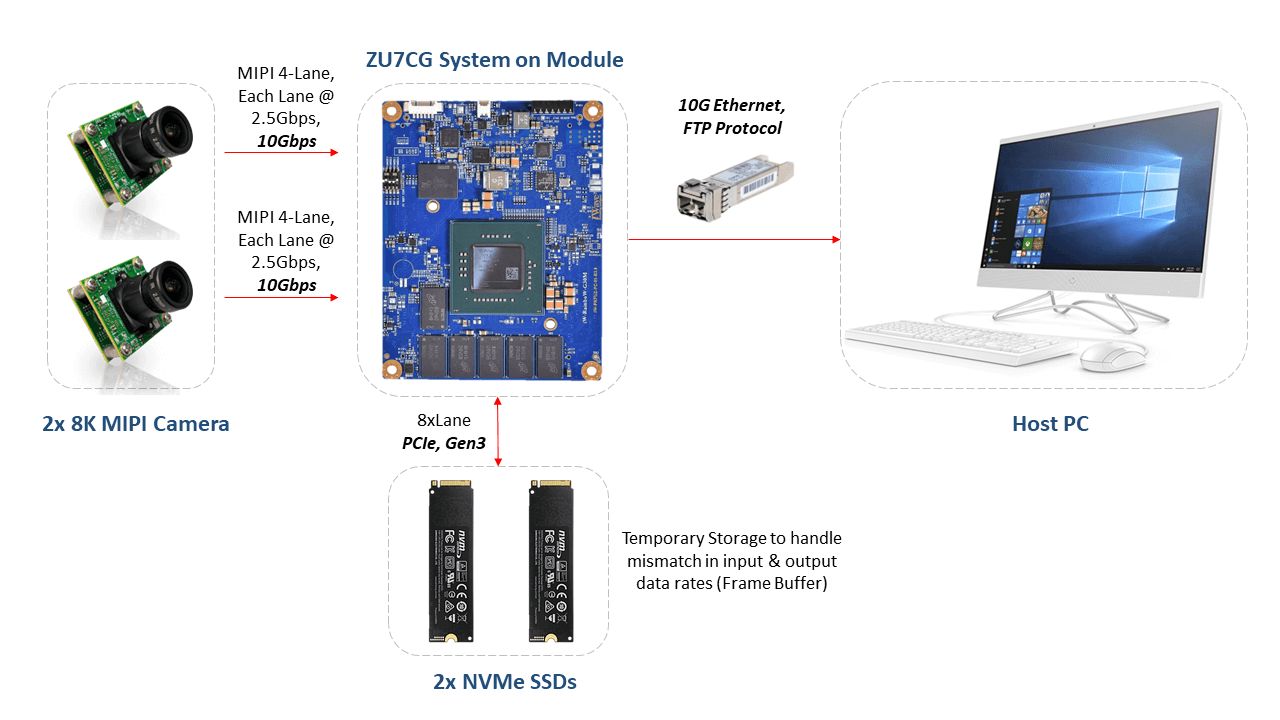

Case Study Designing Ultra Hd Image Acquisition System Using Zynq Ultrascale Mpsoc Devices For Medical Imaging Iwave Systems

Snickerdoodle Xilinx Zynq Arm Fpga Board Starts At 55 Crowdfunding Cnx Software

I Mx 8m Plus Pico Itx Sbc Iwave Systems

Fpga Soc Teknologi I Dag Og I Fremtiden

Fpgas Fpga Cpu News

I Mx 8m Quad Quadlite Dual Smarc Som Iwave Systems

Telecommunications

Xilinx Zynq 7000 Myc C7z015 Cpu Module Function Block Diagram Design Solutions Linux Solutions

Layerscape Ls1021a Smarc Som Iwave Systems

How To Understand The Term Clock Region In Xilinx Fpga Quora